Logische Bauelemente aus CMOS-Bausteinen

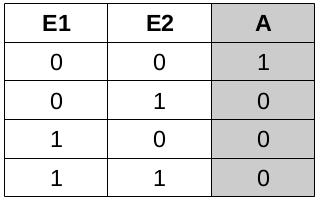

Um die Übersicht zu behalten, sei hier kurz erwähnt, dass das letzte Kapitel von der zweiten Schicht im Hardware-Schichtenmodell, der „elektrischen Ebene“, handelte. (Die erste Schicht, die „physikalische Ebene“ ist Sache der Physik und wird hier selbstverständlich nicht weiter diskutiert.) Das NOT-Gatter allerdings war der erste Schritt in die dritte Schicht, die „logische Ebene“. Man darf nicht vergessen, dass alle Daten als Potenziale gespeichert sind. Ein „logischer Baustein“ hat daher die Aufgabe, die Potenziale logisch miteinander zu verknüpfen. Ein einfaches Beispiel: E1 und E2 mögen Aussagen sein, wie „Mittwoch schreibt man im Deutschen mit zwei t“ und „Samstag schreibt man im Deutschen mit zwei m“. Der ersten wahren Aussage ordnet man den Wert 1 zu, der zweiten unwahren Aussage den Wert 0. In der Tabelle rechts ist A die Aussage „E1 und zugleich E2“ (E1 AND E2). Daher muss A hier eine 0 zugeordnet werden, denn A ist ja falsch, wenn eine der Aussagen E1 oder E2 falsch sind.

AND-Verknüpfung

Mathematisch gesehen ist dies eine zweistellige Verknüpfung mit Definitionsmenge {0;1} × {0;1}.

Man kann leicht einsehen, dass es genau sechzehn derartige Verknüpfungen gibt. Eine komplette Aufzählung mit Namen findet man auf Wikipedia.

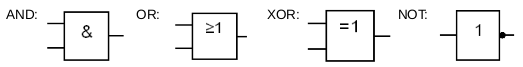

Eine von ihnen ist das nebenstehend dargestellte AND-Gatter; weitere Beispiel sind: OR, NOR, XOR und das NAND- Gatter.

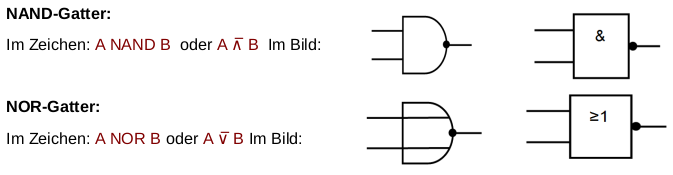

NAND-Gatter

Henry Sheffer bewies 1933, dass man sie alle (inklusive des einstelligen NOT) auf (ggf mehrere) NAND-Gatter reduzieren kann.

Das bedeutet, dass man theoretisch nur ein Bauteil aus CMOS-Bausteinen bauen muss. Alle anderen Verknüpfungen lassen sich aus diesem Einen kombinieren. (Dass man dies aber nicht in allen Fällen tut, hängt damit zusammen, dass dann unnötig viele CMOS-Bausteinen verbaut würden, mit anderen Worten: Es geht oft noch einfacher).

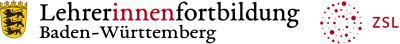

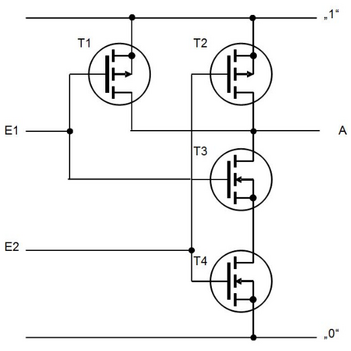

Grund genug, das sagenhaften NAND-Gatter aus n-MOS und p-MOS Bausteinen zu erstellen. Zur Erinnerung:

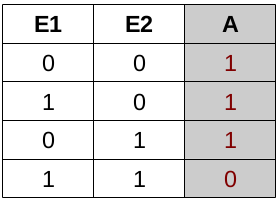

Damit lässt sich jetzt das folgende Schaltbild erklären:

NAND-Gatter in CMOS-Technologie

Eine Tabelle erleichtert die Arbeit (s steht für sperrt, l steht für leitet).

| E1 | T1 (p) | T3 (n) | E2 | T2 (p) | T4 (n) | A |

|---|---|---|---|---|---|---|

| 0 | l | s | 0 | l | s | 1 |

| 0 | l | s | 1 | s | l | 1 |

| 1 | s | l | 0 | l | s | 1 |

| 1 | s | l | 1 | s | l | 0 |

Erläuterung:

Das Eingangssignal E1 ist mit T1 und T3 verbunden. Der besseren Übersicht wegen sind die zugehörigen Spalten nebeneinander angeordnet.

Wenn einer der beiden Bausteinen T3 oder T4 sperrt, kann A nicht an 0 liegen. Es ist dann noch zu prüfen, ob T1 oder T2 leitet. Ansonsten wäre der Zustand undefiniert. Dies trifft auf Zeile 1-3 zu.

In Zeile 4 leiten T3 und T4, während T1 und T2 sperren. An A liegt also eine 1 an.

Mit dem Programm Ciruits kann man die NAND-Schaltung genauer beobachten: e-cmosnand.html

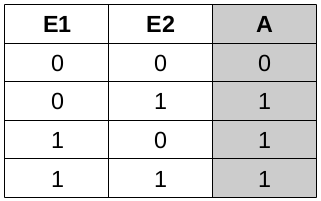

NOR-Schaltung

Aufgabe

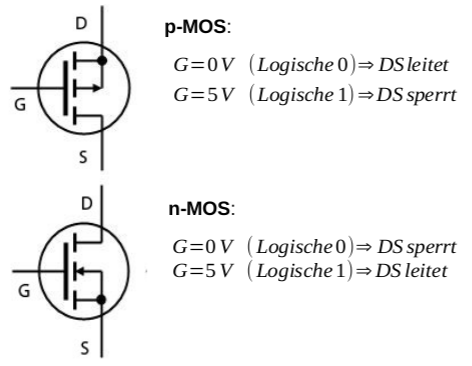

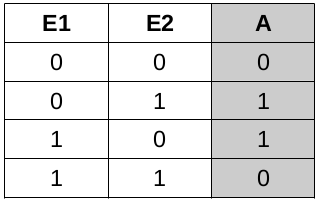

Durch die untenstehende Tabelle wird die sogenannte

NOR-Verknüpfung definiert. Zeigen Sie, dass man sie

durch

die

angegebene Schaltung realisieren kann. Erstellen Sie dazu wie oben

zunächst

eine geeignete Tabelle mit den Schaltzuständen der

MOS-Elemente.

Diese Seite ist hierfür hilfreich: e-cmosnor.html

Auf Dauer ist es etwas unbequem, wenn man bei Verwendung eines NAND- oder NOR-Gatters jedes Mal den vollständigen Schaltplan aufzeichnen muss. Wesentlich ist ja nur, dass es zwei Eingänge, einen Ausgang und eine zugehörige Verknüpfungstabelle gibt. Es gibt leider viele Schaltsymbole für ein und dasselbe Gatter. Hier werden je zwei benutzt: Nach DIN 40700 und nach IEC 60617-12.

In dieser Vereinfachung lassen sich nun die einzelnen Schaltelemente kombinieren, ohne dass man deshalb jeden p-MOS oder n-MOS Baustein eintragen müsste.

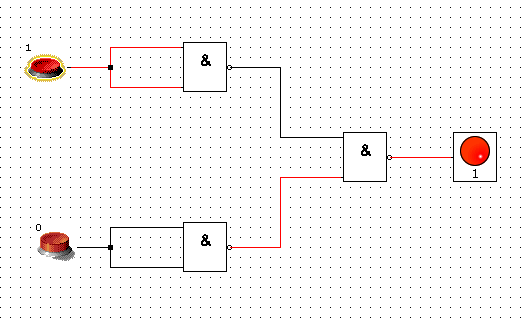

Wenn man die Gatter selbst nicht zur Verfügung hat (und das dürfte der Normalfall in der Schule sein), dann kann man mit den Freewaren Piiri oder LogicSim die Schaltungen simulieren. Im Bild unten ist das NAND- und das NOR-Gatter mit je zwei Eingängen und einer LED verbunden worden. Eine Kabelverbindung kann man erstellen, indem man mit der Maus eine Verbindung zieht. Versuchen Sie es selbst!

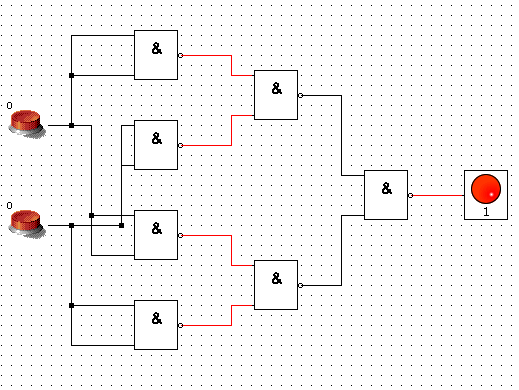

Weiter oben wurde behauptet, dass sich alle zweistelligen logischen Funktionen mit dem NAND-Gatter darstellen lassen. Es wird behauptet:

x NOR y = ((x NAND x) NAND (y NAND y)) NAND ((x NAND x) NAND (y NAND y)) (*)

Mit LogicSim kann man diesen Term in eine Schaltung umsetzen:

NOR-Schaltung aus NAND-Gattern in LogicSim

Weitere Schaltungen: NOT, AND, OR und XOR

Eine wichtige logische Funktion fehlt noch: die OR-Verknüpfung. Gemeint ist nicht das „ausschließende Oder“, wie: „Ich gehe heute Abend entweder ins Kino oder ins Theater.“, sondern wie „Herr Müller ist Mathematiker oder Lehrer“. Dies stimmt auch, wenn Hr. Müller Mathematiker und Lehrer ist.

Man kann OR so durch NAND erzeugen:

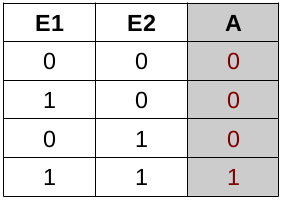

Nicht versessen sollte man, dass wir die Gatter auch verwenden wollen, um Rechnungen durchzuführen. Mit AND kann man immerhin die Multiplikation zweier einstelliger Dualzahlen durchführen. Bei der Addition wird es insofern ein Problem geben, da es mit 1b + 1b = 10b kein einstelliges Ergebnis mehr gibt. Für den Anfang genügt es allerdings, die hintere Stelle der Addition zu berechnen. Und damit ist man bei der XOR-Verknüpfung:

XOR-Verknüpfung

Im Folgenden werden wir die folgenden Symbole verwenden:

Hintergrundinformationen: Herunterladen [odt][4 MB]

Weiter zu Torsteuerung